我们公司专注于芯片解密及其相关技术,同时提供一系列与之相关的服务。我们的专业领域还包括PCB逆向开发、原理图和BOM分析等。通过我们资深工程师团队的10多年实战经验,我们能够以卓越的技术和成功的解决方案在市场上脱颖而出。如果您需要我们的帮助,请随时拨打电话或添加微信联系我们。

一般描述

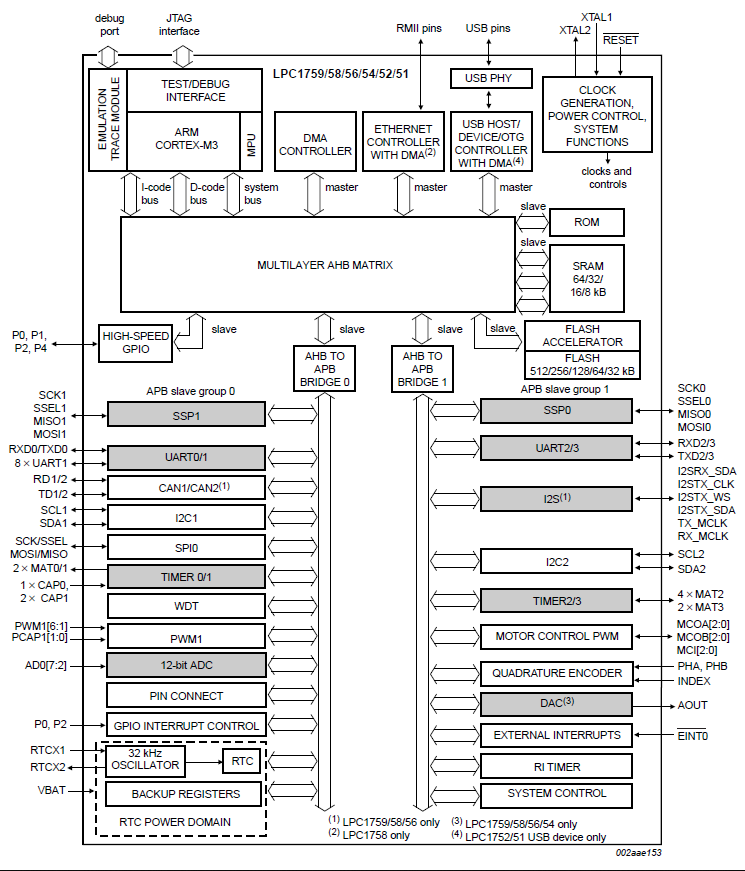

LPC1759/58/56/54/52/51是基于ARM Cortex-M3的微控制器,用于嵌入式应用,具有高度集成和低功耗的特点。ARM Cortex-M3是下一代内核,提供了系统增强功能,如增强的调试功能和更高水平的支持块集成。LPC1758/56/57/54/52/51的CPU工作频率高达100 MHz。LPC1759的CPU工作频率高达120 MHz。ARM Cortex-M3 CPU集成了一个3级流水线,采用哈佛架构,具有独立的本地指令和数据总线,以及用于外设的第三条总线。ARM Cortex-M3 CPU还包括一个内部预取单元,支持推测性分支。LPC1759/58/56/54/52/51的外设包括高达512 kB的闪存、高达64 kB的数据存储器、以太网MAC、USB设备/主机/OTG接口、8通道通用DMA控制器、4个UART、2个CAN通道、2个SSP控制器、SPI接口、2个I2C总线接口、 2输入加2输出的I2S总线接口,6通道12位ADC,10位DAC,电机控制PWM,正交编码器接口,4个通用定时器,6输出通用PWM,带独立电池供电的超低功耗实时时钟(RTC),以及多达52个通用I/O引脚。

特点和优点

ARM Cortex-M3处理器,运行频率高达100 MHz(LPC1758/56/57/54/52/51)或高达120 MHz(LPC1759)。包括一个支持八个区域的内存保护单元(MPU)。

ARM Cortex-M3内置嵌套的矢量中断控制器(NVIC)。

高达512 kB的片上闪存编程存储器。增强型闪存加速器可实现高速120 MHz操作,零等待状态。

通过片上引导程序软件进行系统内编程(ISP)和应用内编程(IAP)。

片上SRAM包括:

在CPU上有高达32 kB的SRAM,具有本地代码/数据总线,用于高性能CPU访问。

两个/一个16 kB的SRAM块,具有独立的访问路径,以提高吞吐量。这些SRAM块可用于以太网(仅LPC1758)、USB和DMA存储器,也可用于通用CPU指令和数据存储。

AHB多层矩阵上的八个通道通用DMA控制器(GPDMA),可用于SSP、I2S总线、UART、模数和数模转换外设、定时器匹配信号,以及用于存储器到存储器的传输。

多层AHB矩阵互连为每个AHB主站提供一个单独的总线。AHB主站包括CPU、通用DMA控制器、以太网MAC(仅LPC1758)和USB接口。这种互连提供没有仲裁延迟的通信。

分离式APB总线允许高吞吐量,在CPU和DMA之间很少出现停顿。

串行接口:

仅在LPC1758上,以太网MAC具有RMII接口和专用DMA控制器。USB 2.0全速设备/主机/OTG控制器具有专用DMA控制器和片上PHY,用于设备、主机和OTG功能。LPC1752/51仅包括一个USB设备控制器。

四个UART,具有小数波特率生成、内部FIFO和DMA支持。一个UART具有调制解调器控制I/O和RS-485/EIA-485支持,一个UART具有IrDA支持。

CAN 2.0B控制器,具有两个(LPC1759/58/56)或一个(LPC1754/52/51)通道。

SPI控制器,具有同步、串行、全双工通信和可编程的数据长度。

两个SSP控制器,具有FIFO和多协议能力。SSP接口可与GPDMA控制器一起使用。

两个I2C总线接口支持快速模式,数据速率为400 kbit/s,具有多地址识别和监控模式。

仅在LPC1759/58/56上,I2S(Inter-IC Sound)接口用于数字音频输入或输出,具有分数率控制。I2S总线接口可与GPDMA一起使用。I2S-总线接口支持3线和4线数据传输和接收,以及主时钟输入/输出。

其他外围设备:

52 通用I/O(GPIO)引脚,具有可配置的上拉/下拉电阻。所有的GPIO都支持一种新的、可配置的开漏工作模式。GPIO块通过AHB多层总线进行快速访问,并位于内存中,从而支持Cortex-M3位带和通用DMA控制器使用。

位模数转换器(ADC),在六个引脚之间进行输入复用,转换率高达200 kHz,并有多个结果寄存器。该12位ADC可与GPDMA控制器一起使用。

仅在LPC1759/58/56/54上,10位数模转换器(DAC)具有专用转换定时器和DMA支持。

四个通用的定时器/计数器,总共有三个捕获输入和十个比较输出。每个定时器块都有一个外部计数输入。可以选择特定的定时器事件来产生DMA请求。

一个电机控制PWM,支持三相电机控制。

正交编码器接口,可监测一个外部正交编码器。

一个标准的PWM/定时器块,具有外部计数输入。

实时时钟(RTC)有一个独立的电源域和专用的RTC振荡器。RTC块包括20字节的电池供电的备份寄存器。

WatchDog Timer (WDT)。WDT可以由内部RC振荡器、RTC振荡器或APB时钟提供时钟。

ARM Cortex-M3系统定时器,包括一个外部时钟输入选项。

重复中断定时器(RIT)提供可编程和重复的定时中断。

每个外设都有自己的时钟分频器,以进一步节省电力。

标准JTAG测试/调试接口,与现有工具兼容。串行线调试和串行线跟踪端口选项。

仿真跟踪模块可以对指令的执行进行非侵入性的高速实时跟踪。

集成的PMU(电源管理单元)自动调整内部调节器,在睡眠、深度睡眠、断电和深度断电模式下将功耗降到最低。

四种降低功率模式: 睡眠、深度睡眠、断电和深度断电。

单个3.3 V电源(2.4 V至3.6 V)。

一个可配置为边缘/电平敏感的外部中断输入。端口0和端口2的所有引脚都可作为边沿敏感的中断源。

无任务中断(NMI)输入。

唤醒中断控制器(WIC)允许CPU从任何优先级中断中自动唤醒,这些中断在深睡眠、断电和深度断电模式下时钟停止时可能发生。

处理器通过任何能够在掉电模式下运行的中断(包括外部中断、RTC中断、USB活动、以太网唤醒中断(仅LPC1758)、CAN总线活动、端口0/2引脚中断和NMI)从掉电模式唤醒。

断电检测,具有独立的中断和强制复位阈值。

通电复位(POR)。

水晶振荡器,工作范围为1 MHz至25 MHz。

4 MHz的内部RC振荡器,精度修整到1%,可选择用作系统时钟。

PLL允许CPU运行到最大的CPU速率,而不需要高频晶体。可以从主振荡器、内部RC振荡器或RTC振荡器中运行。

USB PLL,增加灵活性。

具有不同安全级别的代码读取保护(CRP)。

独特的设备序列号,用于识别目的。

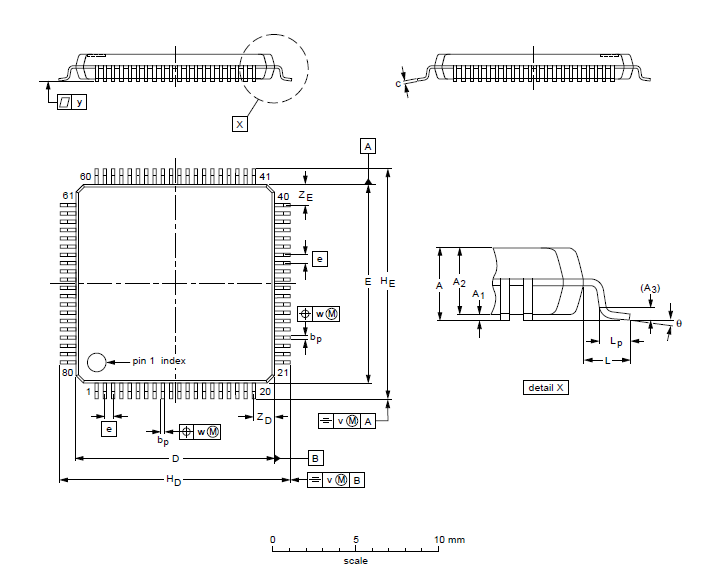

可提供80引脚LQFP封装(12 mm 12 mm 1.4 mm)。

应用

照明 工业网络 报警系统 电机控制

功能框图

包装信息